### Circuits and Devices

### Communications Technology

### Computer

Sponsored by the Test Technology Technical Committee of the IEEE Computer Society

Electromagnetics and Radiation

Energy and Power

**Industrial Applications**

Signals and Applications

Standards Coordinating Committees

# IEEE Standard Test Access Port and Boundary-Scan Architecture

**Sponsor**

# Test Technology Technical Committee of the IEEE Computer Society

Approved February 15, 1990

#### **IEEE Standards Board**

Abstract: IEEE Std 1149.1-1990, IEEE Standard Test Access Port and Boundary—Scan Architecture, defines circuitry that may be built into an integrated circuit to assist in the test, maintenance, and support of assembled printed circuit boards. The circuitry includes a standard interface through which instructions and test data are communicated. A set of test features is defined, including a boundary-scan register, such that the component is able to respond to a minimum set of instructions designed to assist with testing of assembled printed circuit boards.

Copyright (c) 1990 by

The Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street, New York, NY 10017-2394, USA

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

IEEE Standards documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

IEEE Standards documents are adopted by the Institute of Electrical and Electronics Engineers without regard to whether their adoption may involve patents on articles, materials, or processes. Such adoption does not assume any liability to any patent owner, nor does it assume any obligation whatever to parties adopting the standards documents.

#### **Foreword**

(This Foreword is not a part of IEEE Std 1149.1-1990, Standard Test Access Port and Boundary-Scan Architecture.)

This standard defines a test access port and boundary-scan architecture for digital integrated circuits and for the digital portions of mixed analog/digital integrated circuits. The facilities defined by the standard seek to provide a solution to the problem of testing assembled printed circuit boards and other products based on highly complex digital integrated circuits and high-density surface-mounting assembly techniques. They also provide a means of accessing and controlling design-for-test features built into the digital integrated circuits themselves. Such features might, for example, include internal scan paths and self-test functions as well as other features intended to support service applications in the assembled product.

#### Development of IEEE Standard Test Access Port and Boundary-Scan Architecture

The process of developing this standard began in 1985 when the Joint European Test Action Group (JETAG) was formed in Europe. During 1986, this group expanded to include members from both Europe and North America and, as a result, was renamed the Joint Test Action Group (JTAG). Between 1986 and 1988, the JTAG Technical Subcommittee developed and published a series of proposals for a standardized form of boundary-scan. In 1988, the last of these proposals – JTAG Version 2.0 – was offered to the IEEE Testability Bus Standards Committee (P1149) for inclusion in the standard then under development. The Testability Bus Standards Committee accepted this approach. It decided that the JTAG proposal should become the basis of a standard within the Testability Bus family, with the result that the P1149.1 project was initiated. Following these decisions, the JTAG Technical Subcommittee became the core of the IEEE Working Group that developed this standard.

Between 1985 and approval on February 15, 1990, many individuals made valuable contributions to the development of this standard. At the time of approval of this standard, the members of the working group were:

#### Colin M. Maunder, chair and editor Rodham E. Tulloss, vice-chair

| Dilip K. Bhavsar     | Patrick F. McHugh  | Robert J. Russell  |

|----------------------|--------------------|--------------------|

| Vassilios Gerousis   | Johann Maierhofer  | William H. Smith   |

| Grady L. Giles       | Math N. M. Muris   | Michael Tchou      |

| Charles L. Hudson    | Dieter Ohnesorge   | Lee Whetsel        |

| Curtis Jensen        | Stig Oresjo        | Thomas W. Williams |

| Dirk van de Lagemaat | Gordon D. Robinson |                    |

These people were supported by many other individuals from many different organizations who contributed time, administrative effort, and technical suggestions.

In particular, the working group wishes to acknowledge the contributions made by the following individuals:

LaNae Avra Matthias Kaufmann David L. Rutledge Paul Bardell William McAnney Wim Sauerwald Frans P. M. Beenker Bruno Mueller Erwin Trischler Harry Bleeker Paul Ocampo Jon L. Turino William C. Bruce Anwar Osseyran Chantal Vivier Ray Chapman Kenneth P. Parker R.G. Walther Peter Fleming Chi W. Yau Michel Parot Walter Ghisler David Richards Mark Zagorin Najmi Jarwala Derek Roskell

The following people were on the balloting committee that approved this standard for submission to the IEEE Standards Board:

H. Gordon Adshead

Mike Bullock John D. Evans Paul Akins James C. Bussert John M. Ewalt Charles B. Albert Barry Caldwell Patrick Fasang David Alley Gregory Callahan Erik L. Feldman Anthony P. Ambler Bruce Campbell R. Scott Fetherston Allan H. Anderson John C. Caporal Kenneth W. Fisher Kenneth Anderson William Carney Peter Fleming Richard J. Andreano Ralph Cavin Andrew Flint Jack H. Arabian Eduard Cerny Stephen Forde Elmer Arment R. Chandramouli Ernest E. Forster Dave Armstrong Hung Chang Irving B. Frank William D. Atwell, Jr. Ray Chapman Andrew Fraser Chris B. Bagge Wilton R. Chiles Vassilios Gerousis William A. Baker Peter Claydon Grady L. Giles Paul H. Bardell Melvin I. Cohen M. Gisborne Robert W. Bassett Arthur M. Concouvitis Prabhu Goel Frans P.M. Beenker Nigel Crawley Festus Gail Gray Steven Bennett R.S. Crowley D. Greenwood R.G. Bennetts Les Crudele Terence Gregory Prashant Bhangui Christo Da Costa David H. Grimm Christophe Bianchi Scott Davidson Edward B. Hakim Sol L. Black Vincent T. DeBuono John S. Haluska John Blecha Bulent I. Dervisoglu Marius Hancu Harry Bleeker Douglas Doskocil Jeff Hansen Paul Breedlove Samuel Duncan Peter L. Hansen Melvin Breuer L.G. Egan Fred Harrison Alan L. Bridges Samy El-Guebaly Richard Hartman David Brown Yacoub M. El-ziq Vance Harwood William C. Bruce, Jr. Wallace B. Harwood III Steven Elkind Patrick H. Buffet Chris Ellingham Tord Haulin Philip Bullinger Ado Erdal John P. Hayes

Charles Hefner Christian G. Heiter Richard Hennessy Scott Herrington William J. Hery Peter W. Hibson Jack Hilibrand Jim Homer Lee F. Horney II Daniel Hu Andy Huang Charles Hudson Robert Hum Axel Hunger Phu Huynh Najmi Jarwala Curtis Jensen William A. Johnson Edward M. Johnston Nick Kanopoulos William L. Keiner Brian A. Kelley Randy J. Kelsey Javad Khakbaz Robert B. Kieffer L. Kilroy Charles R. Kime Larry Kinney William M. Klein Frances Koo Roger Kozlowski Bruce P. Kraemer Gunter T. Krampl Gerd Kruger Steven Ladd Lak Ming Lam David L. Landis Thomas L. Langford II Bjorn Larsen Johnny LeBlanc Robert Ledbetter Ben H. Lee Raymond M. Lee Wha-Joon Lee Duane G. Leet Robert Lester

Antonio Lioy

Robert Lipp Gordon G. Liu Ulrich Ludemann Bruce H. Luhrs Burt Magen Kenneth D. Mandl Michael Marhoefer James K. Mathewes, Jr. Colin M. Maunder Solomon Max Peter Maxwell John C. McCann Patrick F. McHugh Larry McNaughton Earl J. Meiers John Mick Brent Miller Jose M. Miranda Maurice Mohr Edward J. Moran Larry Moran Hussein T. Mouftah John Moynihan Shridhar K. Mukund Math N. M. Muris Brian T. Murray Benoit Nadeau-Dostie Joseph J. Nahas Lori R. Nelson Huan T. Nguyen Van Minh Nguyen Tom O'Rourke Paul Ocampo Dieter Ohnesorge Wayne Olson Calvin M. Osborne A. Osseyran Kenneth P. Parker Michel Parot Daniel Payne James Pennell Herman H. Plott Kenneth E. Posse Theo J. Powell Paolo Prinetto Lawrence Prucha Jeffrey R. Quay

Edward Ramirez Mark L. Rapier Shishpal Rawat David J. Richards Gordon D. Robinson Lorin Rocks Robert J. Rodio Raul Rodriquez Herman Roopchand Barry C. Rosales Derek Roskell Craig G. Ross, Jr. Ashim Roy Robert J. Russell William E. Russell, Jr. Sergiu Samuel Yvon Savaria Robert S. Schamis James E. Scharf Bengt-Olaf Schneider Teresa M. Schofield Micaela Serra Ravi Shankar Simon J. Shaw Jacob Shuker David M. Siefert Eric Skuldt William J. Smerek Jeffrey N. Smith William H. Smith Arun Somani Fabio Somenzi David Stannard James H. Stewart William Sullivan Jacques Tazartes Michael Tchou Lluis Teres Jacques Tete David W. Thompson Cihan Tinaztepe Jack Trautman Paul C. Tremoulet Erwin Trischler Joseph G. Tront Li-Ching Tsai Rod Tulloss

Jon Turino

Mark E. Turner

Dirk van de Lagemaat

James Van Derwiele

Ronald P. van Riessen

E. Velez

Rudolf E. Vogeli

Zvonko Vranesic

Ronald Wadsack

Malcolm R. Wallace

Bernath Walter

Mats Warne

J. Richard Weger

Lee Whetsel

Harry Whittemore

James Whitten

Brian R. Wilkins

Arthur Willging

T.W. Williams

William J. Wolf

Chi W. Yau

Guenther Zwiehoff

When the IEEE Standards Board approved this standard on February 15, 1990, it had the following membership:

#### Marco W. Migliaro, Chairman

James M. Daly, Vice Chairman

Andrew G. Salem, Secretary

Dennis Bodson

Paul L. Borrill

Fletcher J. Buckley

Allen L. Clapp

Stephen R. Dillon

Donald C. Fleckenstein

Jay Forster\*

Thomas L. Hannan

Kenneth D. Hendrix

John W. Horch

Joseph L. Koepfinger\*

Michael A. Lawler

Donald J. Loughry

John E. May, Jr.

Lawrence V. McCall

L. Bruce McClung

Donald T. Michael\*

Stig Nilsson

Roy T. Oishi

Gary S. Robinson

Terrance R. Whittemore

Donald W. Zipse

<sup>\*</sup>Member Emeritus

### **Contents**

| Cl | apte       | प्र                                                         | Page              |

|----|------------|-------------------------------------------------------------|-------------------|

| 1. | 1.1<br>1.2 | Introduction                                                | 1-1<br>1-1<br>1-1 |

|    | 1.3        | The Use of IEEE Std 1149.1 to Test an Assembled Product     | 1-2               |

|    | 1.4        | The Use of IEEE Std 1149.1 to Achieve Other Test Goals      | 1–5               |

| 2. |            | General Information                                         | 2-1               |

|    | 2.1        | Document Outline                                            | 2-1               |

|    | 2.2        | Conventions                                                 | 2-1               |

|    | 2.3        | Definitions                                                 | 2-2               |

|    | 2.4        | References                                                  | 2-5               |

| 3. |            | The Test Access Port (TAP)                                  | 3-1               |

|    | 3.1        | Connections That Form the Test Access Port (TAP)            | 3-1               |

|    | 3.2        | The Test Clock Input - TCK                                  | 3-1               |

|    | 3.3        | The Test Mode Select Input - TMS                            | 3-2               |

|    | 3.4        | The Test Data Input - TDI                                   | 3-3               |

|    | 3.5        | The Test Data Output - TDO                                  | 3-4               |

|    | 3.6        | The Test Reset Input - TRST*                                | 3-4               |

|    | 3.7        | Interconnection of Components Compatible With This Standard | 3-5               |

| 4. |            | Test Logic Architecture                                     | 4-1               |

|    | 4.1        | Test Logic Design                                           | 4-1               |

|    | 4.2        | Test Logic Realization                                      | 4-3               |

| 5. |            | The TAP Controller                                          | 5-1               |

|    | 5.1        | TAP Controller State Diagram                                | 5-1               |

|    | 5.2        | TAP Controller Operation                                    | 5-8               |

|    | 5.3        | TAP Controller Initialization                               | 5-16              |

| 6. |            | The Instruction Register                                    | 6-1               |

| ٠. | 6.1        | Design and Construction of the Instruction Register         | 6-1               |

|    | 6.2        | Instruction Register Operation                              | 6-2               |

| _  |            | *                                                           |                   |

| 7. |            | Instructions                                                | 7-1               |

|    | 7.1        | Response of the Test Logic to Instructions                  | 7-1               |

|    | 7.2        | Public Instructions                                         | 7-2               |

|    | 7.3<br>7.4 | Private Instructions                                        | 7-3<br>7-3        |

|    | 7.4<br>7.5 | The BYPASS Instruction                                      | 7-3<br>7-5        |

|    | 7.5<br>7.6 | Boundary-Scan Register Instructions                         | 7-3<br>7-9        |

|    | 7.0        | The EXTECT Instruction                                      | 7 12              |

| Chapter            |                                                                                              | Page                 |

|--------------------|----------------------------------------------------------------------------------------------|----------------------|

| 7.8<br>7.9<br>7.10 | The INTEST Instruction The RUNBIST Instruction. Device Identification Register Instructions. | 7-16<br>7-20<br>7-23 |

| 7.11<br>7.12       | The IDCODE Instruction                                                                       | 7-23                 |

| 7.12               | The USERCODE Instruction                                                                     | 7-24                 |

| 8. T               | est Data Registers                                                                           | 8-1                  |

| 8.1                | Provision of Test Data Registers                                                             | 8-1                  |

| 8.2                | Design and Construction of Test Data Registers                                               | 8-3                  |

| 8.3                | Test Data Register Operation                                                                 | 8-5                  |

| 9. T               | he Bypass Register                                                                           | 9–1                  |

| 9.1                | Design and Operation of the Bypass Register                                                  | 9-1                  |

| 10. Ti             |                                                                                              |                      |

| 10.1               | Provision of Roundary San Residence O. H.                                                    | 10-1                 |

| 10.1               | Provision of Boundary-Scan Register Cells                                                    | 10-1                 |

| 10.2               | Implementation of the Boundary-Scan Register                                                 | 10-8                 |

| 10.4               | System Input Pins                                                                            | 10-8                 |

| 10.5               | 2-State System Output Pins.                                                                  | 10-13                |

| 10.6               | 3-State System Output Pins                                                                   | 10-15                |

| 10.7               | Bidirectional System Pins.                                                                   | 10-20<br>10-24       |

| 11. Th             |                                                                                              |                      |

| 11.1               | Design and Operation of the Device Heatifieric B.                                            | 11-1                 |

| 11.2               | Design and Operation of the Device Identification Register                                   | 11-1                 |

| 11.3               | Manufacturer Identity Code                                                                   | 11-3                 |

| 11.4               | Version Code                                                                                 | 11-4                 |

|                    | version code                                                                                 | 11–5                 |

| 12. Co             | onformance and Documentation Requirements                                                    | 12-1                 |

| 12.1               | Claiming Conformance to This Standard                                                        | 12-1                 |

| 12.2<br>12.3       | Prime and Second Source Components                                                           | 12-2                 |

| 12.3               | Documentation Requirements                                                                   | 12-2                 |

| Appendix           |                                                                                              |                      |

| A. Aı              | Example Implementation Using Level-Sensitive Design Techniques                               | A-1                  |

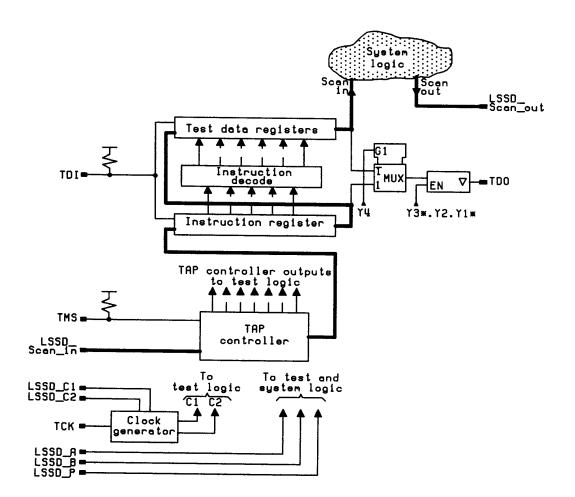

| <b>A.1</b>         | Top-Level Test Logic Design                                                                  | A-1                  |

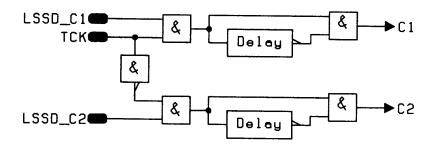

| A.2                | Latch Designs                                                                                | A-4                  |

| A.3                | TAP Controller Implementation                                                                | A-5                  |

| A.4                | Instruction Register Implementation                                                          | A-8                  |

| A.5                | Bypass Register Implementation                                                               | <b>A</b> -9          |

| <b>A</b> .6        | Boundary-Scan Register Implementation                                                        | A-9                  |

## Figures

| Number | Title                                                              | Page  |

|--------|--------------------------------------------------------------------|-------|

| 1-1    | A Boundary-Scan Cell                                               | 1-4   |

| 1-2    | A Boundary-Scannable Board Design                                  | 1-4   |

| 3-1    | Serial Connection Using One TMS Signal                             | 3-6   |

| 3-2    | Connection in Two Paralleled Serial Chains                         | 3-6   |

| 3-3    | Multiple Independent Paths With Common TMS and TCK Signals         | 3-7   |

| 4-1    | A Block Schematic of the Test Logic                                | 4-2   |

| 5-1    | TAP Controller State Diagram                                       | 5-1   |

| 5-2    | Timing of Actions in a Controller State                            | 5-2   |

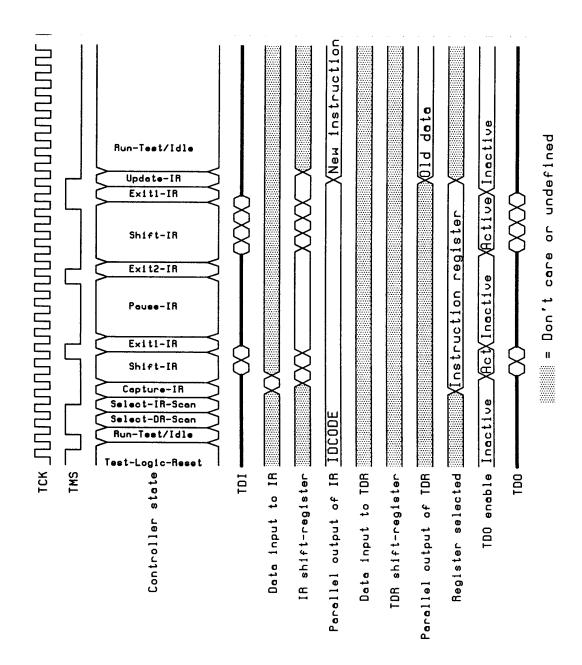

| 5-3    | Test Logic Operation: Instruction Scan                             | 5-9   |

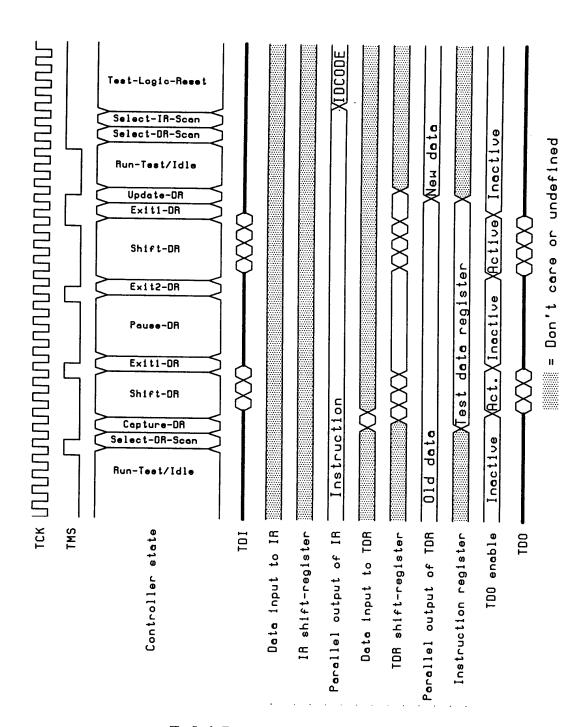

| 5-4    | Test Logic Operation: Data Scan                                    | 5-10  |

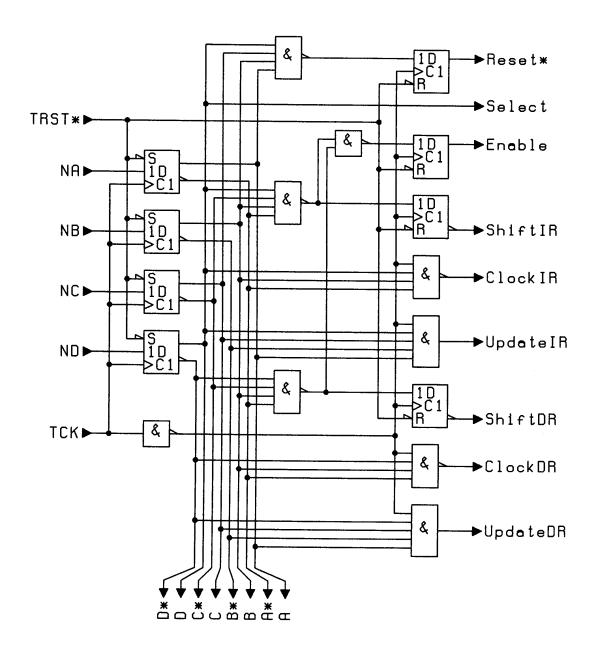

| 5-5    | A TAP Controller Implementation - State Registers and Output Logic | 5-12  |

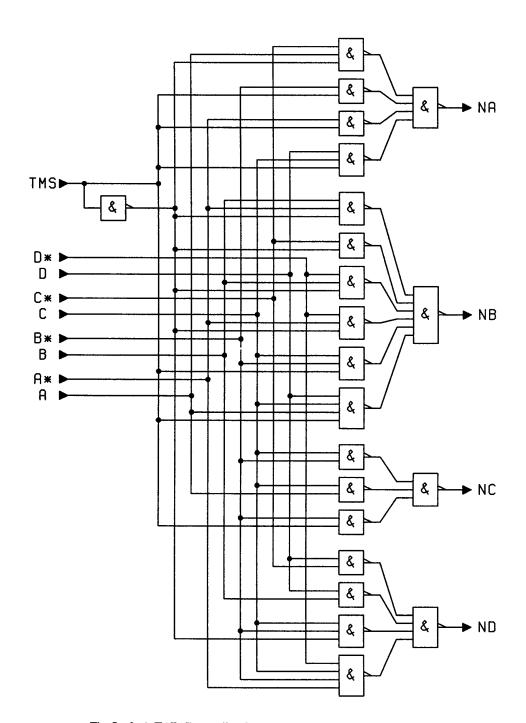

| 5-6    | A TAP Controller Implementation - Next State Logic                 | 5-13  |

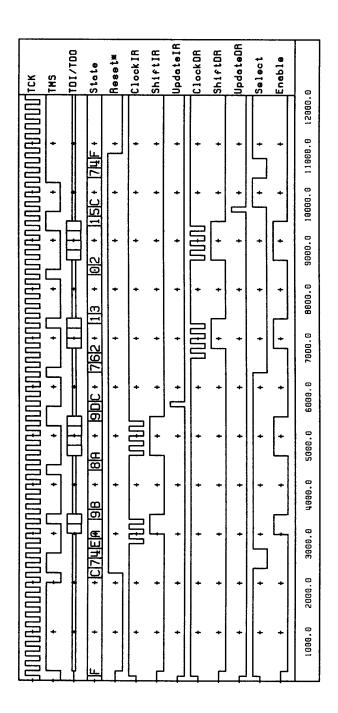

| 5-7    | Operation of the Example TAP Controller                            | 5-15  |

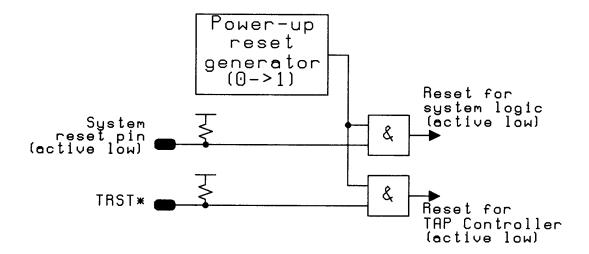

| 5-8    | Use of Power-Up Reset for System and Test Logic                    | 5-17  |

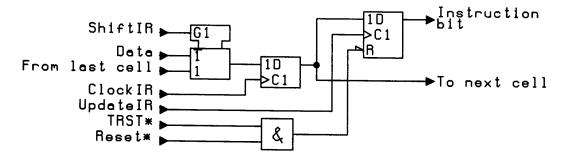

| 6-1    | An Instruction Register Cell                                       | 6-4   |

| 7-1    | A Simplified View of the Boundary-Scan Register                    | 7-5   |

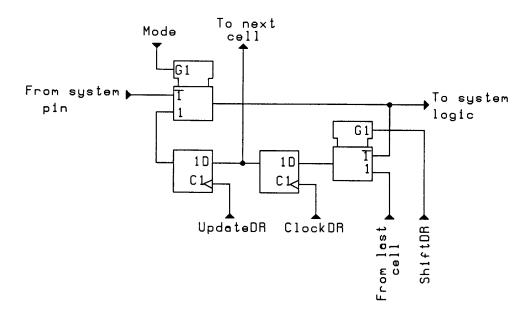

| 7-2    | An Example Boundary-Scan Cell Design                               | 7-6   |

| 7-3    | Circuit Used to Illustrate Boundary-Scan Instructions              | 7-8   |

| 7-4    | Data Flow for the SAMPLE Phase of the SAMPLE/PRELOAD               |       |

|        | Instruction                                                        | 7-11  |

| 7-5    | Data Flow for the PRELOAD Phase of the SAMPLE/PRELOAD              |       |

|        | Instruction                                                        | 7-12  |

| 7-6    | Test Data Flow While the EXTEST Instruction Is Selected            | 7-15  |

| 7-7    | Test Data Flow While the INTEST Instruction Is Selected            | 7-18  |

| 7-8    | Control of Applied System Clock During INTEST                      | 7-19  |

| 7-9    | Use of TCK as Clock for On-Chip System Logic During INTEST         | 7-19  |

| 8-1    | An Implementation of the Group of Test Data Registers              | 8-2   |

| 8-2    | Construction of Test Data Registers From Shared Circuitry          | 8-4   |

| 8-3    | Example Design Containing Two Optional Test Data Registers         | 8-7   |

| 9-1    | A Bypass Register Implementation                                   | 9-1   |

| 10-1   | Terminology                                                        | 10-3  |

| 10-2   | Control of Multiple 3-State Outputs From One Signal                | 10-3  |

| 10-3   | Testing Board-Level Bus Lines                                      | 10-4  |

| 10-4   | Input Pins Used Only to Control Output Pins - Case A               | 10-5  |

| 10-5   | Input Pins Used Only to Control Output Pins - Case B               | 10-6  |

| 10-6   | Illegal Use of a Single Cell for Output Control and Data           | 10-6  |

| 10-7   | A Cell not Permitted in the Boundary-Scan Register                 | 10-7  |

| 10-8   | An Input Cell With Parallel Output Register                        | 10-10 |

| 10-9   | An Input Cell Without Parallel Output Register                     | 10-11 |

| 10-10  | A Cell That Forces the System Logic Input to 1 During EXTEST       | 10-11 |

| 10-11  | An Input Cell Allowing Signal Capture Only                         | 10-12 |

| Number | Title                                                               | Page  |

|--------|---------------------------------------------------------------------|-------|

| 10-12  | A Cell Design That Can Be Used for Both Input and Output Pins       | 10-13 |

| 10-13  | Testing External Logic via the Boundary-Scan Path                   | 10-16 |

| 10-14  | A Primitive Output Cell Design With Potential Problems              | 10-17 |

| 10-15  | Circuit Illustrating Potential Boundary-Scan Test Problem           | 10-17 |

| 10-16  | An Output Cell That Supports All Instructions                       | 10-18 |

| 10-17  | An Output Cell That Supports SAMPLE/PRELOAD, EXTEST, and            |       |

|        | RUNBIST                                                             | 10-19 |

| 10-18  | Boundary-Scan Cells at a 3-State Output - Example 1                 | 10-22 |

| 10-19  | Boundary-Scan Cells at a 3-State Output - Example 2                 | 10-23 |

| 10-20  | Boundary-Scan Cells at a 3-State Pin Where Output Control Is From a |       |

|        | System Pin                                                          | 10-24 |

| 10-21  | Boundary-Scan Cells at a Bidirectional Pin - Example 1              | 10-26 |

| 10-22  | Boundary-Scan Cells at a Bidirectional Pin - Example 2              | 10-27 |

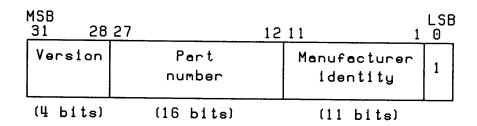

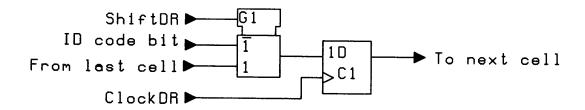

| 11-1   | Structure of the Device Identification Register                     | 11-2  |

| 11-2   | Device Identification Register Cell Design                          | 11-2  |

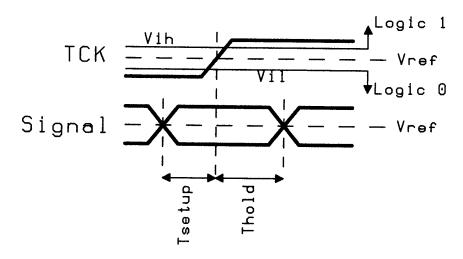

| 12-1   | Measuring Set-Up and Hold Timing                                    | 12-5  |

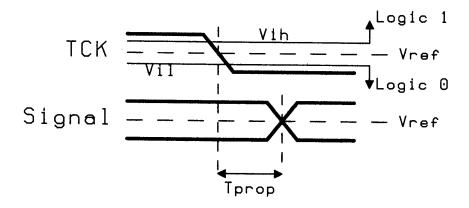

| 12-2   | Measuring Propagation Delays                                        | 12-5  |

| A-1    | Test Logic Schematic                                                | A-2   |

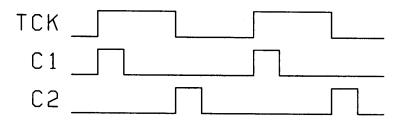

| A-2    | Generation of Nonoverlapping Clocks From TCK                        | A-2   |

| A-3    | Operation of the Clock Generator                                    | A-3   |

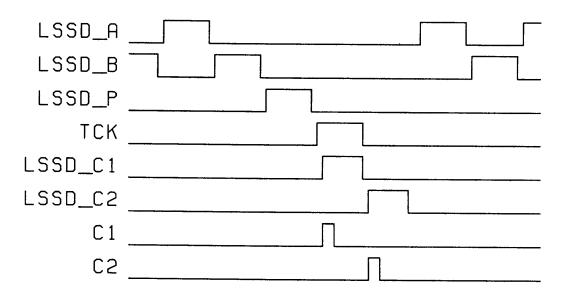

| A-4    | Control of Clocks for "Stand-Alone" Component Testing               | A-3   |

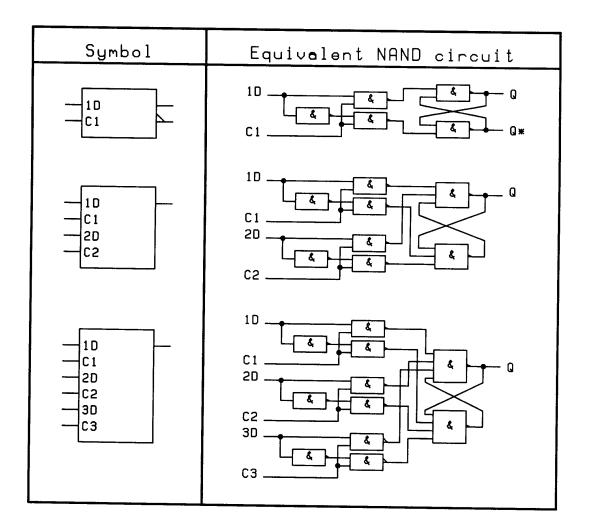

| A-5    | Schematics for Level-Sensitive Latches                              | A-4   |

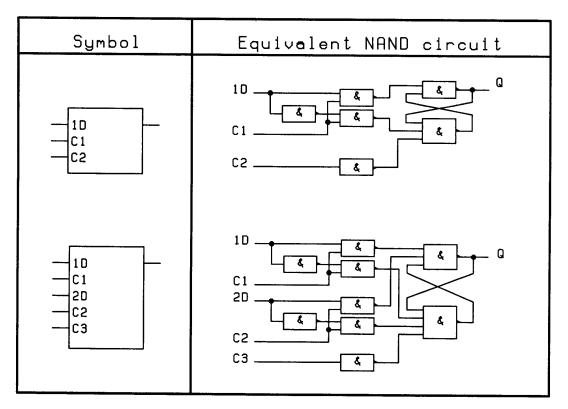

| A-6    | Schematics for Level-Sensitive Latches, Continued                   | A-5   |

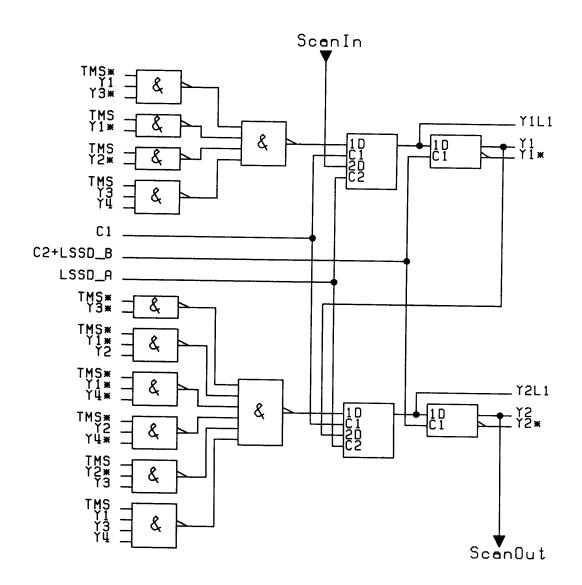

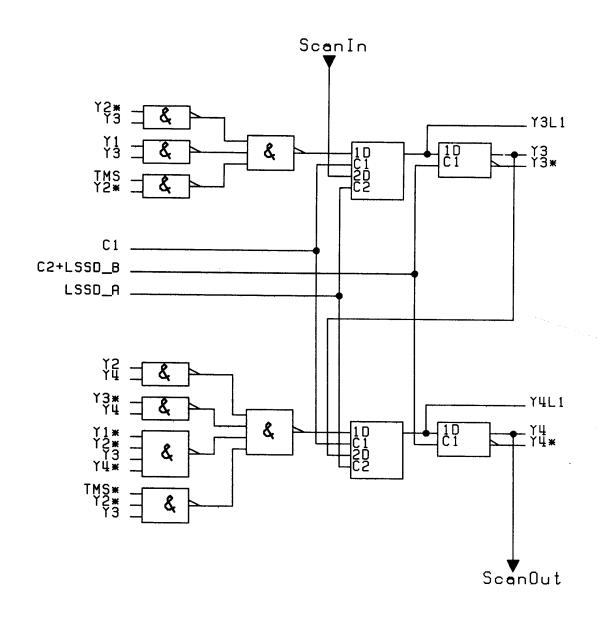

| A-7    | TAP Controller - A                                                  | A-6   |

| A-8    | TAP Controller - B                                                  | A-7   |

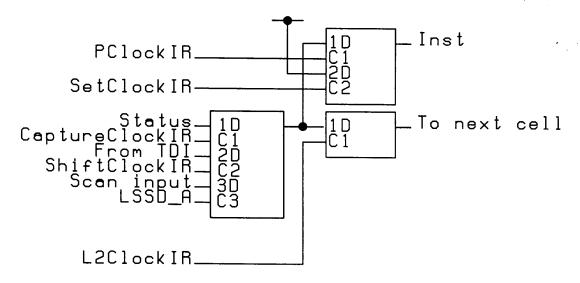

| A-9    | Instruction Register Cell Nearest to TDI                            | A-8   |

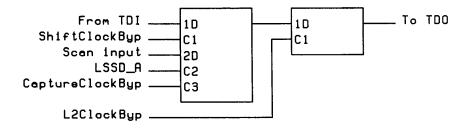

| A-10   | Other Instruction Register Cells                                    | A-8   |

| A-11   | Generation of ResetClock                                            | A-9   |

| A-12   | Bypass Register                                                     | A-9   |

| A-13   | A Level-Sensitive Input Cell Design                                 | A-10  |

| A-14   | A Level-Sensitive Output Cell Design                                | A-10  |

| A-15   | Level-Sensitive Cells at a 3-State Output                           | A-11  |

| A-16   | Level-Sensitive Cells at a Bidirectional Pin                        | Δ_12  |

### **Tables**

| Number | Title                                                                    | Page  |

|--------|--------------------------------------------------------------------------|-------|

| 5-1    | Use of Controller States for Different Test Types                        | 5-7   |

| 5-2    | Test Logic Operation in Each Controller State                            | 5-11  |

| 5-3    | State Assignments for Example TAP Controller                             | 5-14  |

| 6-1    | Instruction Register Operation in Each Controller State                  | 6-3   |

| 8-1    | Naming of Test Data Registers That Share Circuitry                       | 8-5   |

| 8-2    | Operation of the Test Data Register Enabled for Shifting                 | 8-6   |

| 8-3    | Sequential Access to Test Data Registers                                 | 8-8   |

| 10-1   | Test for Driver B                                                        | 10-5  |

| 10-2   | Mode Signal Generation for the Example Cells in Figs 10-8 and 10-9       | 10-10 |

| 10-3   | Mode Signal Generation for the Example Cell in Fig 10-12                 | 10-13 |

| 10-4   | Mode Signal Generation for the Example Cell in Figs 10-16, 10-18, 10-20, |       |

|        | and 10-21                                                                | 10-19 |

| 10-5   | Mode Signal Generation for the Example Cell in Fig 10-17                 | 10-20 |

| 10-6   | Mode Signal Generation for the Example Cell in Fig 10-19                 | 10-23 |

| 10-7   | Mode Signal Generation for the Example Cell in Fig 10-22                 | 10-28 |

| 12-1   | Public Instructions                                                      | 12-1  |

# Chapter 1. Introduction

This standard defines test logic that can be included in an integrated circuit to provide standardized approaches to:

- testing the interconnections between integrated circuits once they have been assembled onto a printed circuit board or other substrate;

- testing the integrated circuit itself; and

- observing or modifying circuit activity during the component's normal operation.

The test logic consists of a boundary-scan register and other building blocks and is accessed through a Test Access Port (TAP).

1.1 Background Reading. Persons who are not familiar with scan test and self-test techniques for digital electronic circuits may find it helpful to consult the following publications prior to reading this standard:

AGRAWAL, V.D. and SETH, S.C., Test generation for VLSI chips, IEEE Computer Society Press, 1988.

BENNETTS, R.G., Design of testable logic circuits, Addison-Wesley, 1984.

EICHELBERGER, E.B. and WILLIAMS, T.W., A logic design structure for LSI testability, *Journal of Design Automation and Fault-Tolerant Computing*, vol. 2, no. 2, May 1978, pp. 165-178.

KONEMANN, B. et al., Built-in logic block observation techniques, *Proceedings of the IEEE Test Conference*, IEEE Computer Society Press, 1979, pp. 37-41.

MICZO, A., Digital logic testing and simulation, Harper & Row, 1986.

1.2 An Overview of the Operation of IEEE Std 1149.1. This section provides a general overview of the operation of a component compatible with this standard and provides a background to the detailed discussion in later chapters.

The circuitry defined by this standard allows test instructions and associated test data to be fed into a component and, subsequently, allows the results of execution of such instructions to be read out. All information (instructions, test data, and test results) is communicated in a serial format.

The sequence of operations would be controlled by a bus master, which could be either an automatic test equipment (ATE) or a component that interfaces to a higher-level test bus as a part of a complete system maintenance architecture. Control is achieved through signals applied to the Test

Mode Select (TMS) and Test Clock (TCK) inputs of the various components connected to the bus master. Starting from an initial state in which the test circuitry defined by this standard is inactive, a typical sequence of operations would be as follows.

The first steps would be, in general, to load serially into the component the instruction code for the particular operation to be performed. The test logic defined by this standard is designed such that the serial movement of instruction information is not apparent to those circuit blocks whose operation is controlled by the instruction. The instruction applied to these blocks changes only on completion of the shifting (instruction load) process.

Once the instruction has been loaded, the selected test circuitry is configured to respond. In some cases, however, it is necessary to load data into the selected test circuitry before a meaningful response can be made. Such data are loaded into the component serially in a manner analogous to the process used previously to load the instruction. Note that the movement of test data has no effect on the instruction present in the test circuitry.

Following execution of the test instruction, based where necessary on supplied data, the results of the test can be examined by shifting data out of the component to or through the bus master.

Note that, in cases where the same test operation is to be repeated but with different data, new test data can be shifted into the component while the test results are shifted out. There is no need for the instruction to be reloaded.

Operation of the test circuitry may proceed by loading and executing several further instructions in a manner similar to that described and would conclude by returning the test circuitry and, where required, on-chip system circuitry to its initial state.

- 1.3 The Use of IEEE Std 1149.1 to Test an Assembled Product. This section outlines the use of the boundary-scan circuitry defined by this standard during the process of testing an assembled product such as a printed circuit board.

- 1.3.1 Board Test Goals. The test problem for any product constructed from a collection of components can be decomposed into three goals:

- (a) To confirm that each component performs its required function;

- (b) To confirm that the components are interconnected in the correct manner; and

- (c) To confirm that the components in the product interact correctly and that the product performs its intended function.

This approach is hierarchic in that it can be applied to a board constructed from integrated circuits, to a system constructed from printed circuit boards, or to a complex integrated circuit constructed from a set of simpler functional modules. To simplify the discussion, this description will henceforth concentrate on the case of an assembled printed circuit board constructed from a collection of digital integrated circuits.

At the board level, goals (a) and (b) are typically achieved using in-circuit test techniques; for goal (c), a functional test is required. However in-circuit test techniques have significant limitations when viewed against evolving surface-mount interconnection technology, for example, the difficulty of making reliable contact to miniaturized features of the printed circuit board using a bed-of-nails fixture. How, then, might the above three test goals be achieved if test access becomes limited to the normal circuit connections, plus a relatively small number of special-purpose test connections?

Considering goal (a), it is clear that the vendor of an integrated circuit used in the board-level design will have an established test methodology for that component. The components could be tested on a proprietary ATE system or using a self-test procedure embedded in the design. Information on the test methodology adopted is typically not available to the component purchaser. Even where self-test modes of operation are known to exist, these may not be documented and therefore are not available to the component user. Alternative sources of test data for the board test engineer may be the component test libraries supplied with in-circuit test systems or the test programs developed by component users for incoming inspection of delivered devices.

Wherever the test data for a component originates, the next step is to use it once the component has been assembled onto the printed circuit board. If access is limited to the normal connections of the assembled circuit, this task may be far from simple. This is particularly true if the surrounding components are complex or if the board designer has tied some of the components' connections to fixed logic levels or has left component pins unconnected. Normally, it will not be possible to test the component in the same way that it was tested in isolation unless an in-circuit test is achievable.

To ensure that built-in test facilities can be used or that pre-existing test patterns can be applied, a framework is needed that can be used to convey test data to or from the boundaries of individual components so that they can be tested as if they were freestanding. This framework will also allow access to and control of built-in test facilities of components. Boundary-scan coupled with a test access bus provides such a framework.

The objective of this standard is to define a boundary-scan architecture that can be adopted as a standard feature of integrated circuit designs, thus allowing the required test framework to be created on assembled printed circuit boards and other products.

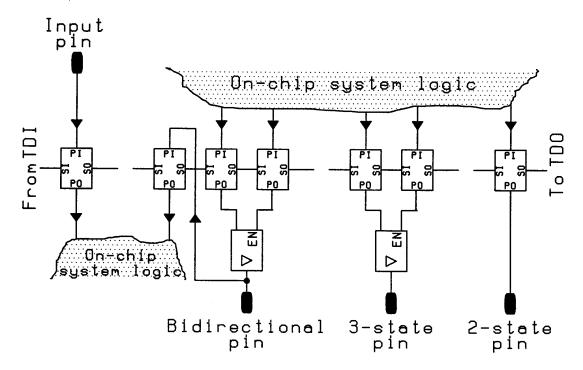

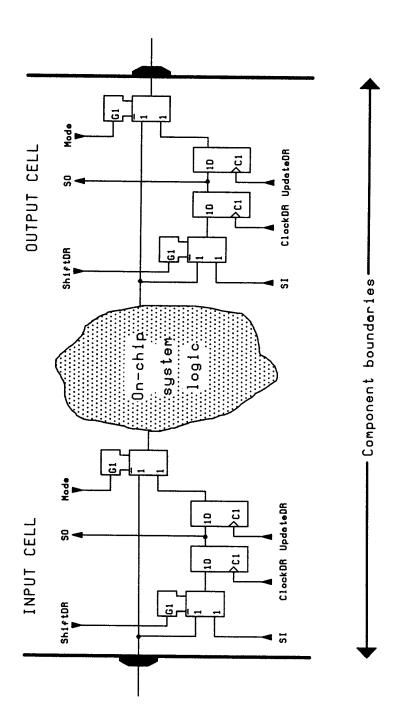

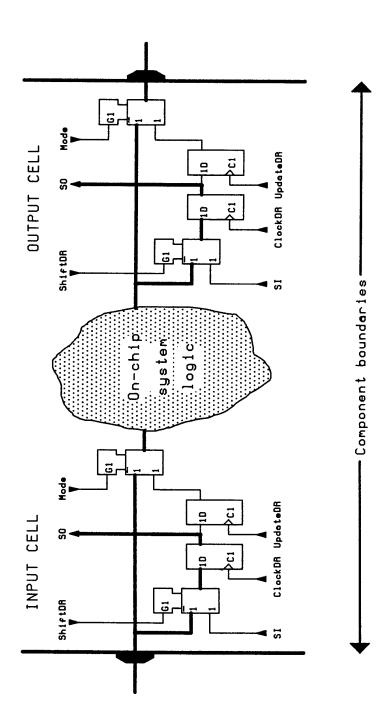

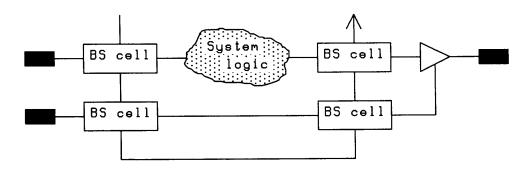

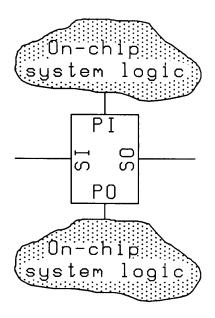

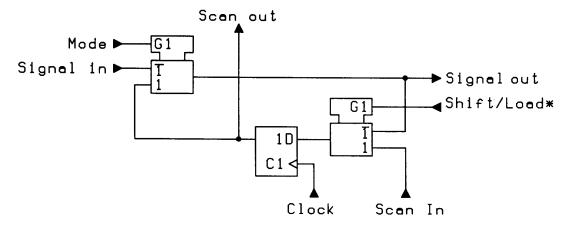

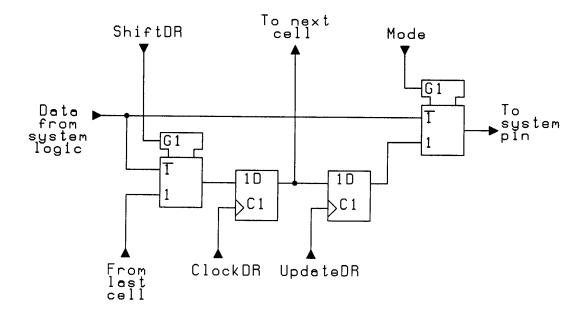

1.3.2 What Is Boundary-Scan? The boundary-scan technique involves the inclusion of a shift-register stage (contained in a boundary-scan cell) adjacent to each component pin so that signals at component boundaries can be controlled and observed using scan testing principles.

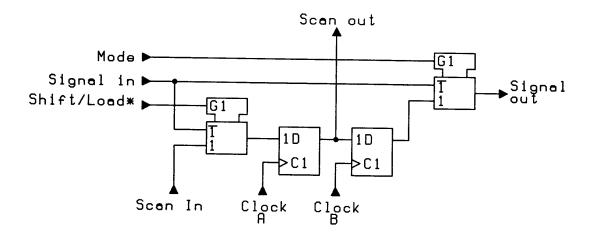

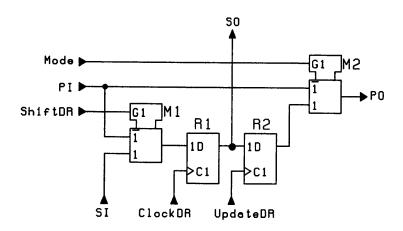

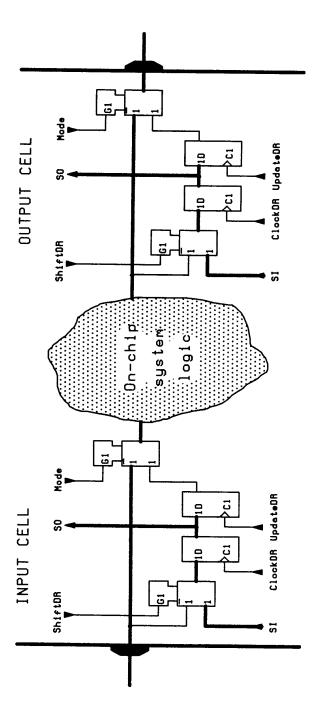

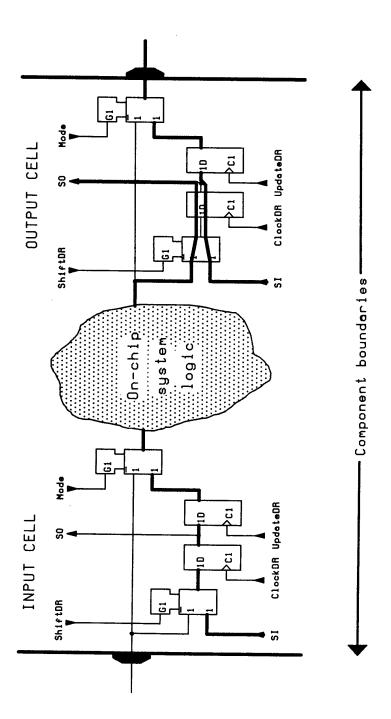

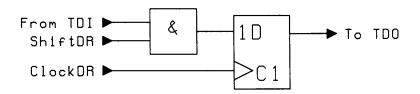

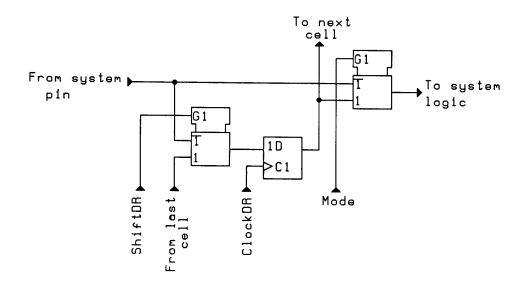

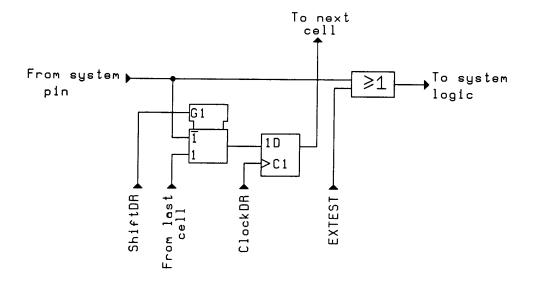

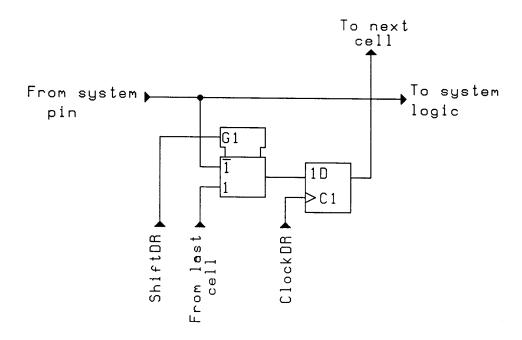

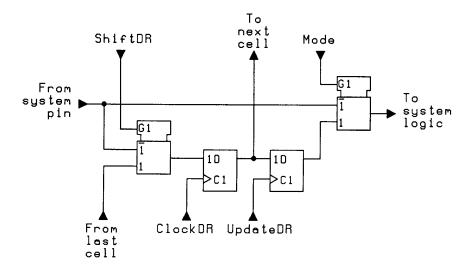

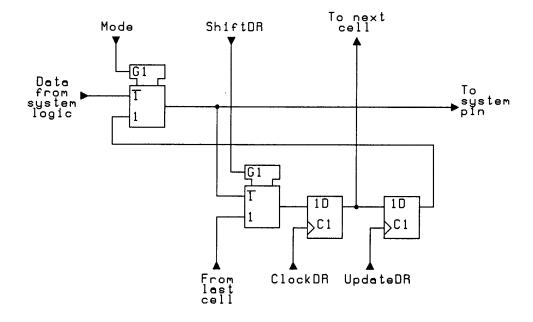

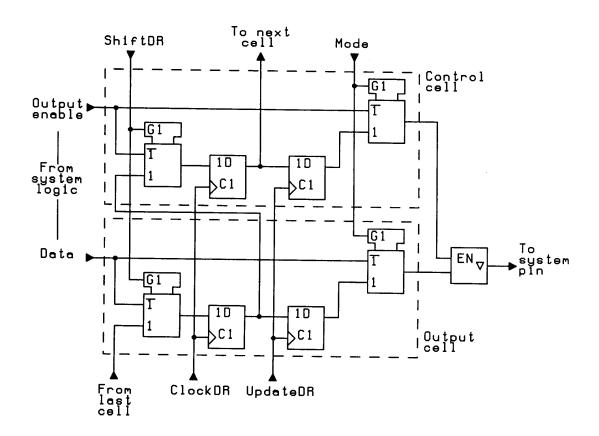

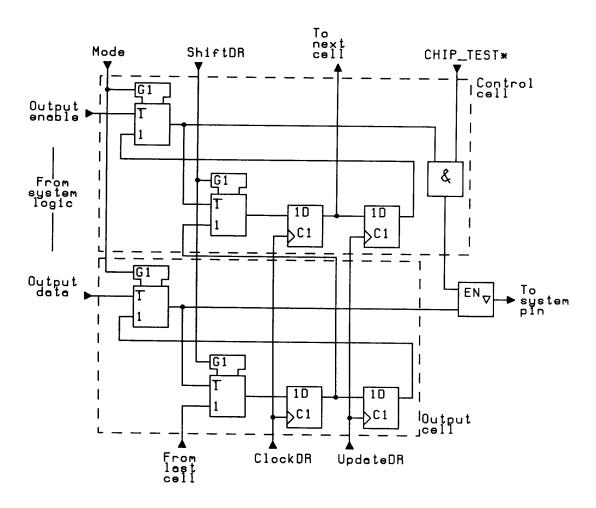

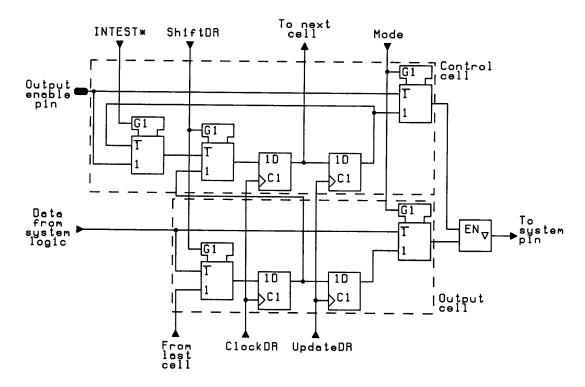

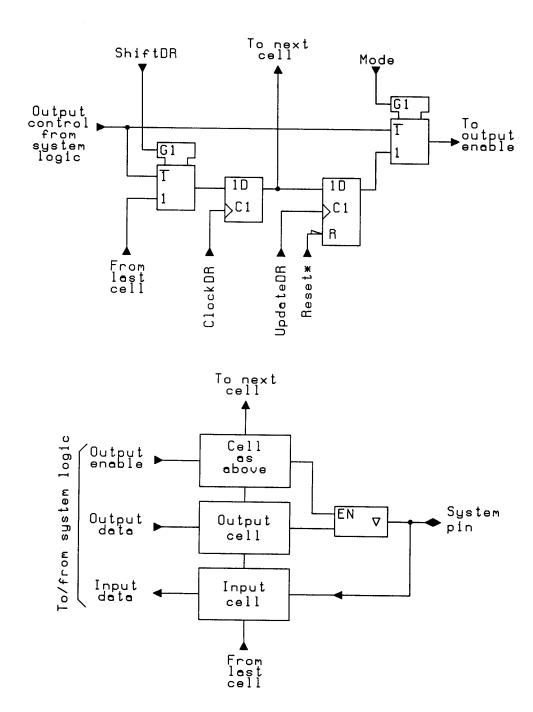

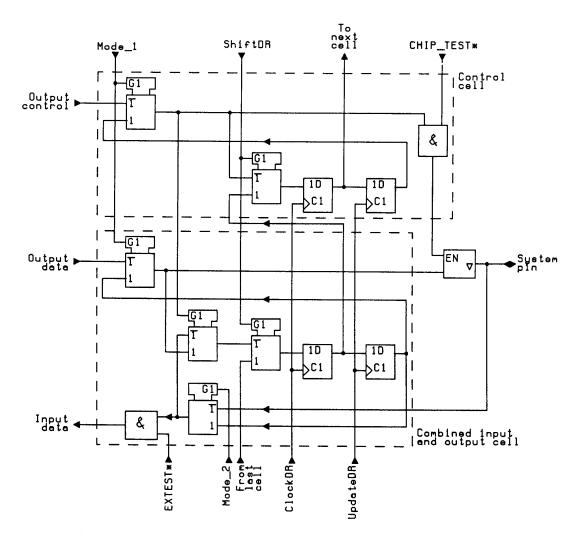

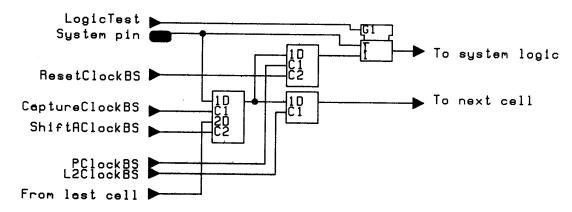

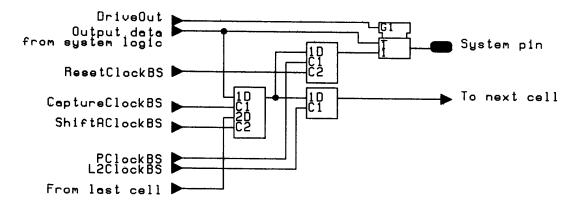

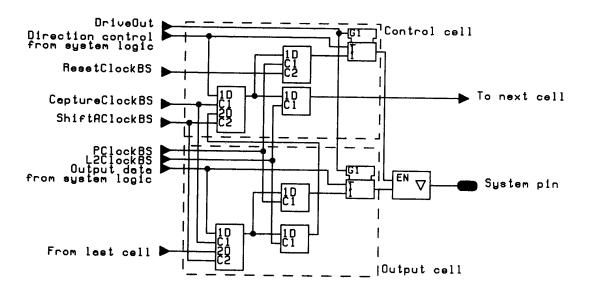

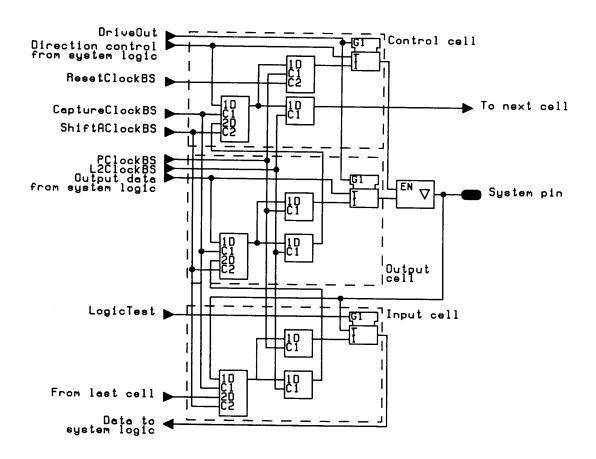

Fig 1-1 illustrates an example implementation for a boundary-scan cell that could be used for an input or output connection to an integrated circuit. Dependent on the control signals applied to the multiplexers, data can either be loaded into the scan register from the Signal-in port (e.g., the input pin), or driven from the register through the Signal-out port of the cell (e.g., into the core of the component design). As will be discussed in detail in Chapter 10, the second flip-flop (controlled by input Clock B) is provided to ensure that the signals driven out of the cell in the latter case are held while new data is shifted into the cell using input Clock A. This flip-flop is not required in all cases, but is included in Fig 1-1 to simplify the discussion.

Fig 1-1 A Boundary-Scan Cell

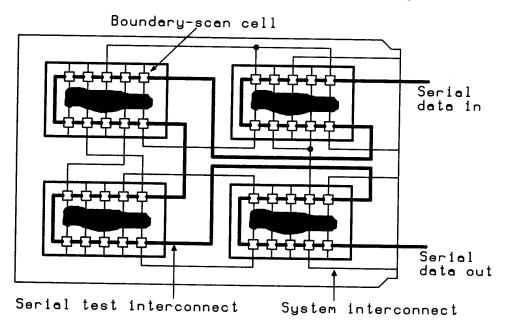

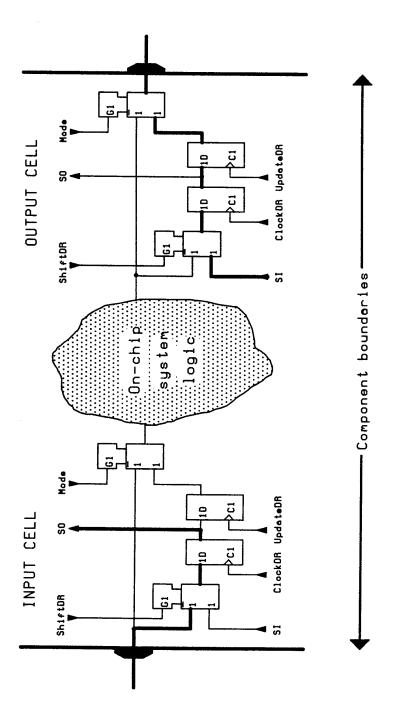

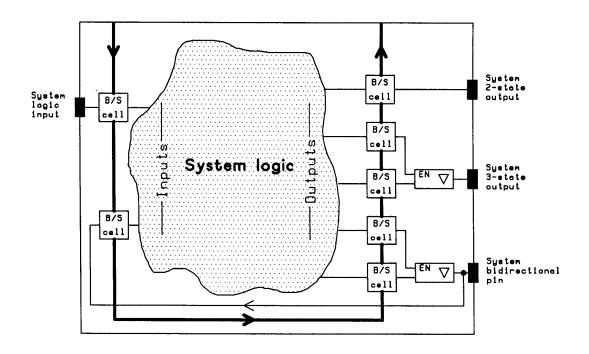

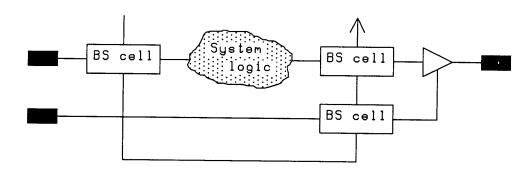

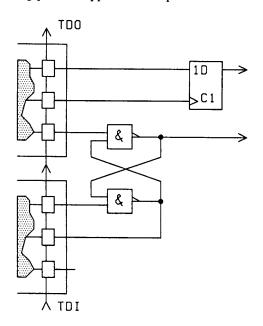

The boundary-scan cells for the pins of a component are interconnected so as to form a shift-register chain around the border of the design, and this path is provided with serial input and output connections and appropriate clock and control signals. Within a product assembled from several integrated circuits the boundary-scan registers for the individual components could be connected in series to form a single path through the complete design, as illustrated in Fig 1-2. Alternatively, a board design could contain several independent boundary-scan paths.

Fig 1-2 A Boundary-Scannable Board Design

If all the components used to construct a circuit have a boundary-scan register, then the resulting serial path through the complete design can be used in two ways:

- (a) To allow the interconnections between the various components to be tested, test data can be shifted into all the boundary-scan register cells associated with component output pins and loaded in parallel through the component interconnections into those cells associated with input pins; and

- (b) To allow the components on the board to be tested, the boundary-scan register can be used as a means of isolating on-chip system logic from stimuli received from surrounding components while an internal self-test is performed. Alternatively, if the boundary-scan register is suitably designed, it can permit a limited slow-speed static test of the on-chip system logic since it allows delivery of test data to the component and examination of the test results.

These tests allow the first two goals discussed earlier to be achieved through the use of the boundary-scan register. In effect, tests applied using the register can detect many of the faults that in-circuit testers currently address, but without the need for extensive bed-of-nails access. The third goal – to functionally test the operation of the complete product – remains and can be achieved either using a functional (through the pins) ATE system or using a system-level self-test, for example.

Note also that by parallel loading the cells at both the inputs and outputs of a component and shifting out the results, the boundary-scan register provides a means of "sampling" the data flowing through a component without interfering with the behavior of the component or the assembled board. This mode of operation is valuable for design debugging and fault diagnosis since it permits examination of connections not normally accessible to the test system.

1.4 The Use of IEEE Std 1149.1 to Achieve Other Test Goals. In addition to its application in testing printed circuit assemblies and other products containing multiple components, the test logic defined by this standard can be used to provide access to a wide range of design-for-test features built into the components themselves. Such features might include internal scan paths, self-test functions [e.g., using built-in logic block observer (BILBO) elements], or other support functions.

Design-for-test features such as these can be accessed and controlled using the data path between the serial test data pins of the TAP defined by this standard. Instructions that cause internal reconfiguration of the component's system logic such that the test operation is enabled may be shifted into the component through the TAP.

# Chapter 2. General Information

2.1 Document Outline. Circuit designs such as that defined by this standard are more easily understood if their specifications are accompanied by general descriptive material that places the details of the various parts of the design in perspective and provides examples of implementation. Chapter 1 therefore contains an overview of the application of this standard to the testing of the digital portions of an electronic product consisting of many integrated circuits.

Subsequent chapters of the document contain the specifications for particular features of this standard. Two classes of material are contained in these chapters:

#### **Specifications**

Subsections entitled Specifications contain the rules, recommendations, and permissions that define this standard:

Rules specify the mandatory aspects of this standard. Clauses that are rules contain the word shall.

<u>Recommendations</u> indicate preferred practice for designs that seek to conform to this standard. Clauses that are recommendations contain the word should.

<u>Permissions</u> show how optional features may be introduced into a design that seeks to conform to this standard. These features will extend the application of the test circuitry defined by the standard. Clauses that are permissions contain the word may.

#### **Descriptions**

Material not contained in subsections entitled Specifications is descriptive material that illustrates the need for the features being specified or their application. This material includes schematics that illustrate a possible implementation of the specifications in this standard. The Appendix to this standard contains an alternative implementation example. The descriptive material also discusses design decisions made during the development of this standard.

NOTE: The descriptive material contained in this standard is for illustrative purposes only and does not define a preferred implementation.

- 2.2 Conventions. The following conventions are used in this standard:

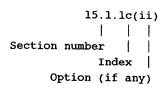

- (a) The rules, recommendations, and permissions in each Specifications subsection are contained in a single alphabetically indexed list. References to each rule, recommendation, or permission are shown in the form:

- (b) Instruction and state names defined in this standard are shown in *italic* type in the text of this standard.

- (c) Names of states and signals that pertain to the test data registers defined by this standard contain the characters DR, while those that pertain to the instruction register contain the characters IR.

- (d) Names for signals that are active in their low state have an asterisk as the final character, e.g., TRST\*.

- (e) A positive logic convention is used, i.e., a logic 1 signal is conveyed as the more positive of the two voltages used for logic signals.

- 2.3 Definitions. The following terms are used within this standard.

- active. When associated with a logic level (e.g., active-low), this term identifies the logic level to which a signal shall be set to cause the defined action to occur. When referring to an output driver (e.g., an active drive), this term describes the state in which the driver is capable of determining the voltage of the network to which it is connected.

- ATE. Automatic Test Equipment.

- bidirectional pin. A component pin that can either drive or receive signals from external connections.

- BILBO. Built In Logic Block Observer. A shift-register based structure used in some forms of self-testing circuit design.

- blind interrogation. Access to a facility (e.g., the device identification register) without prior knowledge of the test logic operation of the specific component being accessed.

- BYPASS. A defined instruction for the test logic defined by this standard (see 7.4).

- chip-on-board testing. A test of a component after it has been assembled onto a printed circuit board or other substrate, for example, using the facilities defined by this standard.

- clock. A signal where transitions between the low and high logic level (or vice-versa) are used to indicate when a stored-state device, such as a flip-flop or latch, may perform an operation.

- EXTEST. External test a defined instruction for the test logic defined by this standard (see 7.7).

- falling edge. A transition from a high to a low logic level. In positive logic, a change from logic 1 to logic 0.

- high. The higher of the two voltages used to convey a single bit of information. For positive logic, a logic 1.

- IDCODE. Identity code a defined instruction for the test logic defined by this standard (see 7.11).

- inactive. When referring to an output driver (e.g., an inactive drive), this term describes the state in which the driver is not capable of determining the voltage of the network to which it is connected.

- input pin. A component pin that receives signals from the external connections.

- instruction. A binary data word shifted serially into the test logic defined by this standard in order to define its subsequent operation.

- INTEST. Internal test a defined instruction for the test logic defined by this standard (see 7.8).

- least significant bit (LSB). The digit in a binary number representing the lowest numerical value. For shift-registers, the bit located nearest to the serial output, or the first bit to be shifted out. The least significant bit of a binary word or shift-register is numbered 0.

- level-sensitive scan design (LSSD). A variant of the scan design technique that results in race-free, testable digital electronic circuits.

- low. The lower of the two voltages used to convey a single bit of information. For positive logic,

- most significant bit (MSB). The digit in a binary number representing the greatest numerical value. For shift-registers, the bit furthest from the serial output, or the last bit to be shifted out. Logic values expressed in binary form are shown with their most significant bit on the left.

- nonclock. A signal where the transitions between the low and high logic levels do not themselves cause operation of stored-state devices. The logic level is important only at the time of a transition on a clock signal.

- output pin. A component pin that drives signals onto external connections.

- pin. The point at which connection is made between the integrated circuit and the substrate on which it is mounted (e.g., the printed circuit board). For packaged components, this would be the package pin; for components mounted directly on the substrate, this would be the bonding pad.

- prime source. In the event that several vendors offer pin-for-pin compatible components, the prime source is the vendor who introduced the component type.

- private. A design feature intended solely for use by the component manufacturer.

- public. A design feature, documented in the component data sheet, that may be used by purchasers of the component.

- rising edge. A transition from a low to a high logic level. In positive logic, a change from logic 0 to logic 1.

- RUNBIST. Run Built-In Self-Test a defined instruction for the test logic defined by this standard (see 7.9).

- SAMPLE/PRELOAD. A defined instruction for the test logic defined by this standard (see 7.6).

- scan design. A design technique that introduces shift-register paths into digital electronic circuits and thereby improves their testability.

- scan path. The shift-register path through a circuit designed using the scan design technique.

- second source. In the event that several vendors offer pin-for-pin compatible components, second-source suppliers are vendors of the component other than the prime source.

- selected test data register. A test data register is selected when it is required to operate by an instruction supplied to the test logic.

- signature analysis. A technique for compressing a sequence of logic values output from a circuit under test into a small number of bits of data (signature) that, when compared to stored data, will indicate the presence or absence of faults in the circuit.

- stand-alone testing. A test of a component performed before it is assembled onto a board or other substrate, for example, using ATE.

- stuck-at fault. A failure in a logic circuit that causes a signal connection to be fixed at 0 or 1 regardless of the operation of the circuitry that drives it.

- system. Pertaining to the nontest function of the circuit.

- system logic. Any item of logic that is dedicated to realizing the nontest function of the component or is at the time of interest configured to achieve some aspect of the nontest function.

- system pin. A component pin that feeds, or is fed from, the on-chip system logic.

- TAP. The Test Access Port defined by this standard (see Chapter 3).

- TCK. The Test Clock input pin contained in the TAP defined by this standard (see 3.2).

- TDI. The Test Data Input pin contained in the TAP defined by this standard (see 3.4).

- TDO. The Test Data Output pin contained in the TAP defined by this standard (see 3.5).

- test logic. Any item of logic that is a dedicated part of the test logic architecture defined by this standard or is at the time of interest configured as a part of the test logic architecture defined by this standard.

- TMS. The Test Mode Select input pin contained in the TAP defined by this standard (see 3.3).

- TRST\*. The Test Reset input pin contained in the TAP defined by this standard (see 3.6).

- TTL. Transistor Transistor Logic.

- USERCODE. User identity code a defined instruction for the test logic defined by this standard (see 7.12).

- 3-state pin. A component output pin where the drive may be either active or inactive (for example, at high impedance).

- 2.4 References. The following publications shall be used in conjunction with this standard. When standards in this document are referred to, the latest revision shall apply.

- [1] JEDEC Publication 106-A, Standard Manufacturer's Identification Code, The Joint Electron Device Engineering Council, July 1986.

<sup>1</sup> Copies can be obtained from JEDEC, 2001 I Street NW, Washington D.C. 20006, USA.

# Chapter 3. The Test Access Port (TAP)

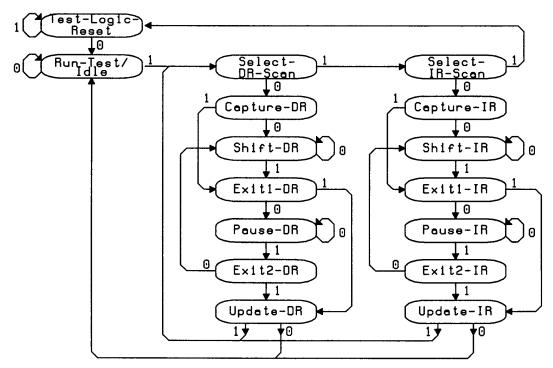

The TAP is a general-purpose port that can provide access to many test support functions built into a component, including the test logic defined by this standard. It is composed as a minimum of the three input connections and one output connection required by the test logic defined by this standard. An optional fourth input connection provides for asynchronous initialization of the test logic defined by this standard.

### 3.1 Connections That Form the Test Access Port (TAP)

#### 3.1.1 Specifications

#### Rules

- (a) The TAP shall include the following connections (defined in 3.2, 3.3, 3.4, and 3.5): TÇK, TMS, TDI, and TDO.

- (b) Where the TAP controller is not reset at power-up as a result of features built into the test logic, a TRST\* input shall be provided as defined in 3.6 (see also 5.3).

- (c) All TAP inputs and outputs shall be dedicated connections to the component (i.e., the pins used shall not be used for any other purpose).

- 3.1.2 Description. Dedicated TAP connections are required to allow access to the full range of mandatory features of this standard.

- 3.2 The Test Clock Input TCK. TCK provides the clock for the test logic defined by this standard.

#### 3.2.1 Specifications

#### Rules

(a) Stored-state devices contained in the test logic shall retain their state indefinitely when the signal applied to TCK is stopped at 0.

#### Recommendations

(b) Since TCK inputs for many components may be controlled from a single driver, care should be taken to ensure that the load presented by TCK is as small as possible.

#### **Permissions**

- (c) Stored-state devices contained in the test logic may retain their state indefinitely when the signal applied to TCK is stopped at 1.

- 3.2.2 Description. The dedicated TCK input is included so that the serial test data path between components can be used independently of component-specific system clocks, which may vary significantly in frequency from one component to the next. It also permits shifting of test data concurrently with system operation of the component. The latter facility is required to support the use of the TAP and test data registers in a design for on-line system monitoring. The provision of an independent clock ensures that test data can be moved to or from a chip without changing the state of the on-chip system logic. The independent clock is also essential if boundary-scan registers are to be usable for board interconnect testing in all circumstances including cases where system clock signals are derived in one component for use in others.

While TCK will in many cases be driven by a free-running clock with a nominal 50% duty cycle, there may be situations where the clock needs to stop for a period. One example is when an ATE needs to fetch test data from backup memory (e.g., disc), since some test systems are unable to keep the clock running during such an operation. This standard requires that TCK can be stopped at 0 indefinitely without causing any change to the state of the test logic. While the TCK signal is stopped at 0, stored-state devices are required to retain their state so that the test logic may continue its operation when clock operation restarts. Optionally, a component may also allow TCK to be stopped at 1 for an indefinite period.

3.3 The Test Mode Select Input - TMS. The signal received at TMS is decoded by the TAP controller to control test operations.

#### 3.3.1 Specifications

#### Rules

- (a) The signal presented at TMS shall be sampled by the test logic on the rising edge of TCK.

- (b) The design of the circuitry fed from TMS shall be such that an undriven input produces a response identical to the application of a logic 1.

#### Recommendations

(c) Since the TMS inputs for many components may be controlled from a single driver, care should be taken to ensure that the load presented by TMS is as small as possible.

3.3.2 Description. Rule 3.3.1b is included so that the TAP controller is forced into the Test-Logic-Reset controller state in the case of an undriven TMS pin. This ensures that normal operation of the complete design can continue without interference from the test logic (see 5.3). For TTL-compatible designs, the rule may be met by including a pull-up resistor in the component's TMS input circuitry.

Signal values presented at TMS are sampled by the test logic on the rising edge of TCK. It is expected that the bus master (ATE, bus controller, etc.) will change the signal driven to the TMS inputs of connected components on the falling edge of TCK. The waveforms shown elsewhere in this standard reflect this expectation.

3.4 The Test Data Input - TDI. Serial test instructions and data are received by the test logic at TDI.

#### 3.4.1 Specifications

#### Rules

- (a) The signal presented at TDI shall be sampled into the test logic on the rising edge of TCK.

- (b) The design of the circuitry fed from TDI shall be such that an undriven input produces a response identical to the application of a logic 1.

- (c) When data is being shifted from TDI towards TDO, test data received at TDI shall appear without inversion at TDO following a number of rising and falling edges of TCK determined by the length of the instruction or test data register selected.

- 3.4.2 Description. The data pins (TDI and TDO) provide for serial movement of test data through the circuit. The requirement for data to be propagated from TDI to TDO without inversion is included to simplify the operation of components compatible with this standard linked on a printed circuit board.

Values presented at TDI are clocked into the selected register (instruction or test data) on a rising edge of TCK. It is expected that the bus master (ATE, bus controller, etc.) will change the signal driven to the TDI input of the first component on a serial board-level path on the falling edge of TCK. The waveforms shown elsewhere in this standard reflect this expectation.

Rule 3.4.1b is included so that open-circuit faults in the board-level serial test data path cause a defined logic value to be shifted into the test logic. Note that when this constant value is shifted into the instruction register the bypass register will be selected (as will be discussed further in 7.4). For TTL-compatible designs, this rule may be met by inclusion of a pull-up resistor in the component's TDI input circuitry.

3.5 The Test Data Output - TDO. TDO is the serial output for test instructions and data from the test logic defined in this standard.

#### 3.5.1 Specifications

#### Rules

- (a) Changes in the state of the signal driven through TDO shall occur only following the falling edge of TCK.

- (b) The TDO driver shall be set to its inactive drive state except when the scanning of data is in progress (see 5.2).

- 3.5.2 Description. To ensure race-free operation, changes on TAP inputs (TMS and TDI) are clocked into the test logic defined by this standard on the rising edge of TCK while changes at the TAP output (TDO) occur on the falling edge of TCK. Similarly, for test logic able to drive or receive signals from system pins (e.g., the boundary-scan register), signals driven out of the component from the test logic change state on the falling edge of TCK, while those entering the test logic are clocked in on the rising edge (as will be discussed in 8.3).

The contents of the selected register (instruction or data) are shifted out of TDO on the falling edge of TCK. In the illustrations given in this document, edge-operated circuit designs are generally used. For an edge-operated implementation, note that the TDO output changes shall be delayed until the falling edge of TCK, which can be achieved by including a flip-flop clocked by the falling edge of TCK in the TDO output buffer. Where the registers are constructed from master and slave latches controlled by non-overlapping clocks, the retiming required by rule 3.5.1a is an inherent feature of the design.

The capability of TDO to switch between active and inactive drive is required to allow parallel, rather than serial, connection of board-level test data paths in cases where this is required. In TTL or CMOS technologies, for example, this requirement may be met through use of a 3-state output buffer.

3.6 The Test Reset Input - TRST\*. The optional TRST\* input provides for asynchronous initialization of the TAP controller (see 5.3).

#### 3.6.1 Specifications

#### Rules

(a) If TRST\* is included in the TAP, then the TAP controller shall be asynchronously reset to the *Test-Logic-Reset* controller state when a logic 0 is applied to TRST\* (see 5.3).

NOTE: As a result of this event, all other test logic in the component is asynchronously reset to the state required in the *Test-Logic-Reset* controller state.

- (b) If TRST\* is included in the TAP, then the design of the circuitry fed from that input shall be such that an undriven input produces a response identical to the application of a logic 1.

- (c) TRST\* shall not be used to initialize any system logic within the component.

#### Recommendations

- (d) To ensure deterministic operation of the test logic, TMS should be held at 1 while the signal applied at TRST\* changes from 0 to 1.

- 3.6.2 Description. Initialization of the TAP controller in turn causes asynchronous initialization of other test logic included in the design, as discussed in the subsequent chapters of this standard.

- Rule 3.6.1b is included to ensure that, in the case of an unterminated TRST\* input, test logic operation can proceed under control of signals applied at the TMS and TCK inputs.

- Rule 3.6.1c ensures that the test logic can be reset independently of the on-chip system logic. This allows the test logic to be disabled by hard-wiring TRST\* to logic 0.

Recommendation 3.6.1d is included to ensure that the test logic responds predictably when the signal applied to TRST\* changes from 0 to 1. If rising edges occur simultaneously at TRST\* and TCK when a logic 0 is applied to TMS, a race will occur, and the TAP controller may either remain in the Test-Logic-Reset controller state or enter the Run-Test/Idle controller state.

#### 3.7 Interconnection of Components Compatible With This Standard

#### 3.7.1 Specifications

#### **Permissions**

- (a) The TAP input and output connections may be interconnected at the board level in a manner appropriate to the assembled product.

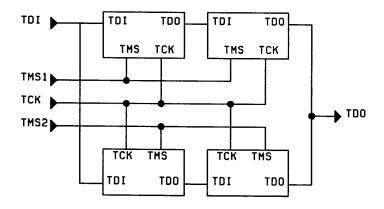

- 3.7.2 Description. Figs 3-1, 3-2, and 3-3 illustrate three alternative board-level interconnections of components conforming to this standard.

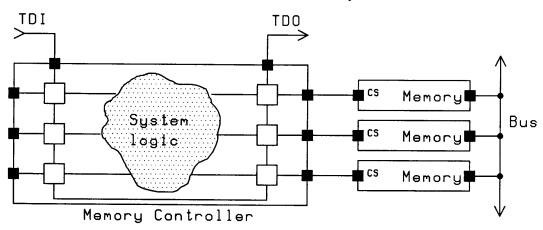

In each example, the test bus may be controlled either by an ATE system or by a component that provides an interface to a test bus at the next level of product assembly (for example, at the board/backplane interface). In this standard, the device that controls the board-level test bus is referred to as the bus master.

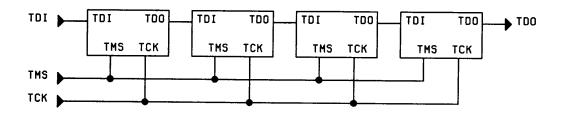

Note that the minimum configuration (shown in Fig 3-1) contains:

(a) Two broadcast signals (TMS and TCK) fed from the testability bus master to all slaves in parallel; and

(b) A serial path formed by a daisy-chain connection of the serial test data pins (TDI and TDO).

Fig 3-1 Serial Connection Using One TMS Signal

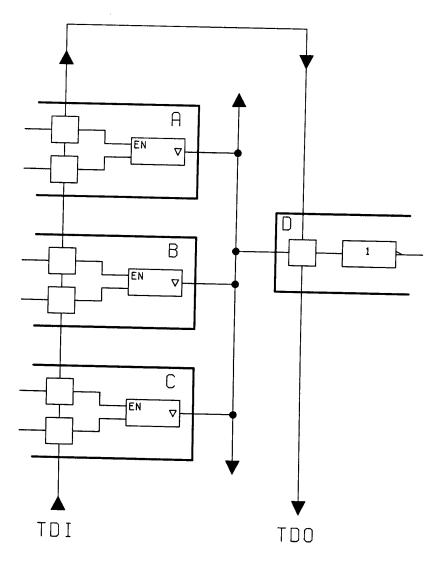

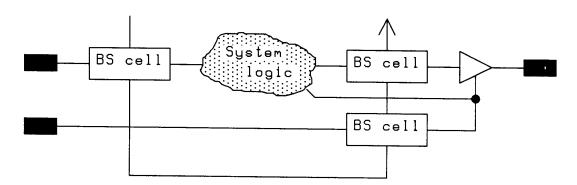

The hybrid serial/parallel connection shown in Fig 3-2 uses a pair of coordinated TMS signals (TMS1 and TMS2) to ensure that only one serial path is scanning data at a given time. This configuration makes use of the 3-state feature of the TDO output pin, which ensures that only the components that are scanning data have TDO in the active drive state.

Fig 3-2 Connection in Two Paralleled Serial Chains

Fig 3-3 shows the four components connected to give four separate serial paths through the complete board design. These paths have separate TDI and TDO signals, but can be controlled from common TCK and TMS signals.

Fig 3-3 Multiple Independent Paths With Common TMS and TCK Signals

# Chapter 4. Test Logic Architecture

This chapter defines the top-level design of the test logic accessed through the TAP. Detailed design requirements for the various blocks contained within the test logic design are contained in the subsequent chapters of this standard.

#### 4.1 Test Logic Design

#### 4.1.1 Specifications

#### Rules

- (a) The following elements shall be contained in the test logic architecture:

- (i) A TAP (see Chapter 3);

- (ii) A TAP controller (see Chapter 5);

- (iii) An instruction register (see Chapter 6); and

- (iv) A group of test data registers (see Chapter 8).

- (b) The instruction and test data registers shall be separate shift-register based paths that are connected in parallel and have a common serial data input and a common serial data output connected to the TAP TDI and TDO signals respectively.

- (c) The selection between the alternative instruction and test data register paths between TDI and TDO shall be made under the control of the TAP controller, as defined in 5.2.

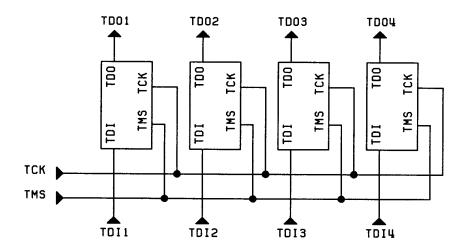

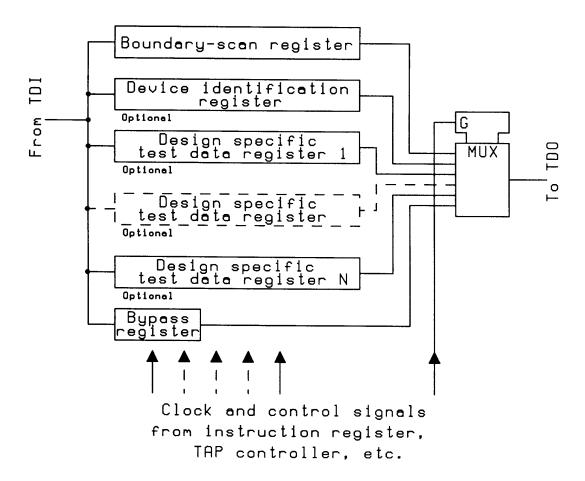

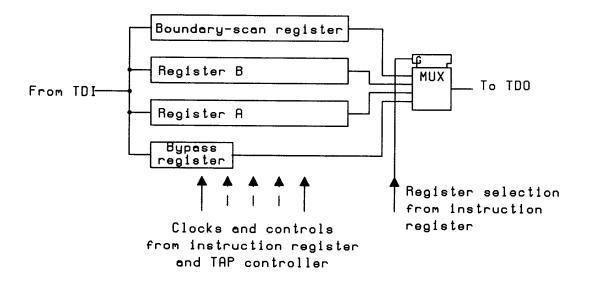

- 4.1.2 Description. A schematic view of the top-level design of the test logic architecture defined by this standard is shown in Fig 4-1. This figure, and the others included in the descriptive material contained in this standard, are examples intended only to illustrate a possible embodiment of the standard. These figures do not indicate a preferred implementation.

Key features of the design are:

- (a) The TAP controller. This receives TCK and interprets the signals on TMS. The TAP controller generates clock or control signals or both as required for the instruction and test data registers and for other parts of the architecture. The specification for the TAP controller is contained in Chapter 5.

- (b) The instruction register. This allows the instruction to be shifted into the design. The instruction is used to select the test to be performed or the test data register to be accessed or both. The specification for the instruction register is contained in Chapter 6.

Fig 4-1 A Block Schematic of the Test Logic

(c) The group of test data registers. The group of test data registers shall include a bypass and a boundary-scan register. It may also include an optional device identification register and further optional test data registers. Further information on the structure of the group of test data registers is contained in Chapter 8.

#### 4.2 Test Logic Realization

#### 4.2.1 Specifications

#### Rules

- (a) The TAP controller, the instruction register, and the associated circuitry necessary for control of the instruction and test data registers shall be dedicated test logic (i.e., these test logic blocks shall not perform any system function).

- (b) If test access is required to a test data register without causing any interference to the operation of the on-chip system logic, then the circuitry used to construct that test data register shall be dedicated test logic.

- 4.2.2 Description. While the example implementations contained in this standard show the various test data registers to be separate physical entities, circuitry may be shared between the test data registers provided the rules contained in this standard are met. For example, this would allow the device identification register and the boundary-scan register to share shift-register stages, in which case the requirements of this standard would be met by operating the common circuitry in two different modes the device identification register mode and the boundary-scan register mode.

# Chapter 5. The TAP Controller

The TAP controller is a synchronous finite state machine that responds to changes at the TMS and TCK signals of the TAP and controls the sequence of operations of the circuitry defined by this standard.

### 5.1 TAP Controller State Diagram

#### 5.1.1 Specifications

#### Rules

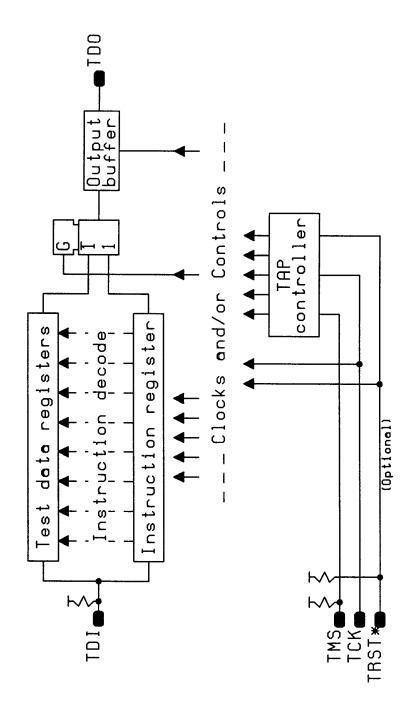

(a) The state diagram for the TAP controller shall be as shown in Fig 5-1.

NOTE: The value shown adjacent to each state transition in this figure represents the signal present at TMS at the time of a rising edge at TCK.

Fig 5-1 TAP Controller State Diagram

- (b) All state transitions of the TAP controller shall occur based on the value of TMS at the time of a rising edge of TCK.

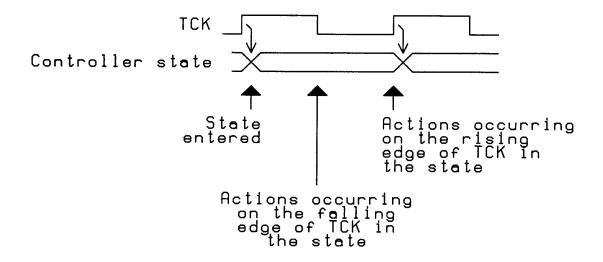

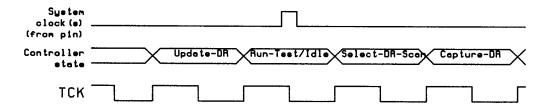

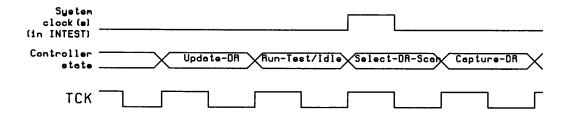

- (c) Actions of the test logic (instruction register, test data registers, etc.) shall occur on either the rising or the falling edge of TCK in each controller state as shown by Fig 5-2.

Fig 5-2 Timing of Actions in a Controller State

5.1.2 Description. The behavior of the TAP controller and other test logic in each of the controller states is briefly described as follows. Rules governing the behavior of the test logic defined by this standard in each controller state are contained in later chapters of this standard.

#### Test-Logic-Reset

The test logic is disabled so that normal operation of the on-chip system logic (i.e., in response to stimuli received through the system pins only) can continue unhindered. This is achieved by initializing the instruction register to contain the *IDCODE* instruction or, if the optional device identification register is not provided, the *BYPASS* instruction (see 6.2). No matter what the original state of the controller, it will enter *Test-Logic-Reset* when TMS is held high for at least five rising edges of TCK. The controller remains in this state while TMS is high.

If the controller should leave the *Test-Logic-Reset* controller state as a result of an erroneous low signal on the TMS line at the time of a rising edge on TCK (for example, a glitch due to external interference), it will return to the *Test-Logic-Reset* state following three rising edges of TCK with the TMS line at the intended high logic level. The operation of the test logic is such that no disturbance is caused to on-chip system logic

operation as the result of such an error. On leaving the Test-Logic-Reset controller state, the controller moves into the Run-Test/Idle controller state where no action will occur because the current instruction has been set to select operation of the device identification or bypass register (see 6.2). The test logic is also inactive in the Select-DR-Scan and Select-IR-Scan controller states.

Note that the TAP controller will also be forced to the *Test-Logic-Reset* controller state by applying a low logic level at TRST\*, if such is provided, or at power-up (see 5.3).

#### Run-Test/Idle

A controller state between scan operations. Once entered, the controller will remain in the Run-Test/Idle state as long as TMS is held low. When TMS is high and a rising edge is applied at TCK, the controller moves to the Select-DR-Scan state.

In the Run-Test/Idle controller state, activity in selected test logic occurs only when certain instructions are present. For example, the RUNBIST instruction causes a self-test of the on-chip system logic to execute in this state (see 7.9). Self-tests selected by instructions other than RUNBIST may also be designed to execute while the controller is in this state.

For instructions that do not cause functions to execute in the Run-Test/Idle controller state, all test data registers selected by the current instruction shall retain their previous state (i.e., Idle).

The instruction does not change while the TAP controller is in this state.

#### Select-DR-Scan

This is a temporary controller state in which all test data registers selected by the current instruction retain their previous state.

If TMS is held low and a rising edge is applied to TCK when the controller is in this state, then the controller moves into the Capture-DR state and a scan sequence for the selected test data register is initiated. If TMS is held high and a rising edge is applied to TCK, the controller moves on to the Select-IR-Scan state.

The instruction does not change while the TAP controller is in this state.

#### Select-IR-Scan

This is a temporary controller state in which all test data registers selected by the current instruction retain their previous state.

If TMS is held low and a rising edge is applied to TCK when the controller is in this state, then the controller moves into the *Capture-IR* state and a scan sequence for the instruction register is initiated. If TMS is held high and a rising edge is applied to TCK,

the controller returns to the Test-Logic-Reset state.

The instruction does not change while the TAP controller is in this state.

#### Capture-DR

In this controller state data may be parallel-loaded into test data registers selected by the current instruction on the rising edge of TCK. If a test data register selected by the current instruction does not have a parallel input, or if capturing is not required for the selected test, then the register retains its previous state unchanged.

The instruction does not change while the TAP controller is in this state.

When the TAP controller is in this state and a rising edge is applied to TCK, the controller enters either the Exit1-DR state if TMS is held at 1 or the Shift-DR state if TMS is held at 0.

#### Shift-DR

In this controller state, the test data register connected between TDI and TDO as a result of the current instruction shifts data one stage towards its serial output on each rising edge of TCK. Test data registers that are selected by the current instruction, but are not placed in the serial path, retain their previous state unchanged.

The instruction does not change while the TAP controller is in this state.

When the TAP controller is in this state and a rising edge is applied to TCK, the controller enters either the ExitI-DR state if TMS is held at 1 or remains in the Shift-DR state if TMS is held at 0.

#### Exit1-DR

This is a temporary controller state. If TMS is held high, a rising edge applied to TCK while in this state causes the controller to enter the Update-DR state, which terminates the scanning process. If TMS is held low and a rising edge is applied to TCK, the controller enters the Pause-DR state.

All test data registers selected by the current instruction retain their previous state unchanged.

The instruction does not change while the TAP controller is in this state.

#### Pause-DR

This controller state allows shifting of the test data register in the serial path between TDI and TDO to be temporarily halted. All test data registers selected by the current instruction retain their previous state unchanged.

The controller remains in this state while TMS is low. When TMS goes high and a rising edge is applied to TCK, the controller moves on to the Exit2-DR state.

The instruction does not change while the TAP controller is in this state.

#### Exit2-DR

This is a temporary controller state. If TMS is held high and a rising edge is applied to TCK while in this state, the scanning process terminates and the TAP controller enters the Update-DR controller state. If TMS is held low and a rising edge is applied to TCK, the controller enters the Shift-DR state.

All test data registers selected by the current instruction retain their previous state unchanged.

The instruction does not change while the TAP controller is in this state.

#### <u>Update – DR</u>

Some test data registers may be provided with a latched parallel output to prevent changes at the parallel output while data is shifted in the associated shift-register path in response to certain instructions (e.g., EXTEST, INTEST, and RUNBIST). Data is latched onto the parallel output of these test data registers from the shift-register path on the falling edge of TCK in the Update-DR controller state. The data held at the latched parallel output should not change other than in this controller state unless operation during the execution of a self-test is required (e.g., during the Run-Test/Idle controller state in response to a design-specific public instruction).

All shift-register stages in test data registers selected by the current instruction retain their previous state unchanged.

The instruction does not change while the TAP controller is in this state.

When the TAP controller is in this state and a rising edge is applied to TCK, the controller enters either the Select-DR-Scan state if TMS is held at 1 or the Run-Test/Idle state if TMS is held at 0.

#### Capture-IR

In this controller state the shift-register contained in the instruction register loads a pattern of fixed logic values on the rising edge of TCK. In addition, design-specific data may be loaded into shift-register stages that are not required to be set to fixed values (see Chapter 6).

Test data registers selected by the current instruction retain their previous state. The instruction does not change while the TAP controller is in this state.

When the TAP controller is in this state and a rising edge is applied to TCK, the controller enters either the ExitI-IR state if TMS is held at 1 or the Shift-IR state if TMS is held at 0.

#### Shift-IR

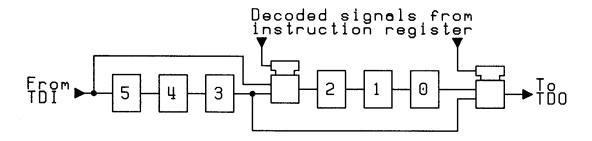

In this controller state the shift-register contained in the instruction register is connected between TDI and TDO and shifts data one stage towards its serial output on each rising edge of TCK.